MOS 6502

| MOS 6502 Central processing unit | |

|---|---|

| |

| Prodotto | 1975 |

| Progettato da | MOS Technology |

| Applicazioni | home computer, arcade |

| Specifiche tecniche | |

| Frequenza CPU | 1 MHz / 2 MHz |

| Set di istruzioni | MOS 6502 |

| Microarchitettura | 8 bit |

| Package | DIP40 |

Il MOS 6502 è un microprocessore a 8 bit presentato da MOS Technology nel settembre del 1975.

Assieme allo Zilog Z80 del luglio 1976 venne usato in molti prodotti commercializzati tra la fine degli anni settanta e gli anni ottanta, come giochi arcade e console domestiche, personal ed home computer, quali l'Apple II ed il Commodore VIC-20.[1] Venne prodotto su licenza da molte ditte, fra cui Rockwell International e Synertek. Dal MOS 6502 derivano diversi processori, tra cui si annoverano il MOS 6507, usato nella console Atari 2600, il MOS 6509, usato nella linea di computer Commodore CBM, ed il MOS 6510, utilizzato come CPU del Commodore 64.[2][3]

Storia

[modifica | modifica wikitesto]Le origini e il progetto in Motorola

[modifica | modifica wikitesto]

Il chip fu progettato dallo stesso gruppo che aveva sviluppato il MOS 6501 e che comprendeva diversi degli ingegneri che avevano lavorato dal 1971 sul Motorola 6800, tra cui Chuck Peddle e Bill Mensch, usciti in massa da Motorola nel 1974.[4]

Peddle aveva promosso commercialmente il 6800 ed aveva visitato molti potenziali clienti per presentare il microprocessore, pensato per un impiego in sistemi embedded. Nonostante le favorevoli impressioni, il processore non vendeva come previsto perché il prezzo di lancio di 360$ era considerato eccessivamente alto: molti clienti consideravano equo un prezzo di $ 25 a chip. Peddle propose perciò a Motorola di sviluppare una versione depotenziata del 6800 da poter vendere a quel prezzo, ma la dirigenza non accolse il suo suggerimento.[5][6][7]

Nonostante il disinteresse dei vertici societari, Peddle iniziò per proprio conto a lavorare a quell'idea. Il nuovo processore era simile al 6800: come questo usava pochi registri ma aveva un solo accumulatore (il 6800 ne aveva 2: registri A e B). Rispetto al 6800, il 6502 introduceva diversi nuovi modi di indirizzamento, permettendo di utilizzare i suoi registri indice e lo stack in maniera molto efficiente: ad esempio, con lo stack era possibile accedere alle celle di memoria poste nell'intervallo di indirizzo 256-511 (esadecimale: $100-$1FF), mentre alcune istruzioni potevano accedere direttamente alle celle di memoria nell'intervallo 0-255 (esadecimale: $00-$FF), la cosiddetta "pagina zero", utilizzando 1 solo byte come indirizzo.[8] Il nuovo chip era inoltre capace di eseguire calcoli in aritmetica BCD (Binary-coded decimal)[9] ed aveva un generatore di clock interno.[10]

Nonostante la disapprovazione dei vertici di Motorola, il gruppo guidato da Peddle continuava a lavorare sul progetto, cominciando a maturare nel contempo malcontento per l'assenza di supporto che ricevevano. Alla fine, la dirigenza decise di fermare lo sviluppo del nuovo chip: come risposta, Peddle e molti dei suoi colleghi lasciarono Motorola alla ricerca di una società che fosse stata interessata a produrre tale chip.[6]

Gli sviluppatori del 6800 passano in MOS Technology

[modifica | modifica wikitesto]Peddle prese contatti con MOS Technology, all'epoca una piccola azienda produttrice di circuiti integrati, fondata da Allen-Bradley per produrre processori per calcolatrici elettroniche per conto di Texas Instruments, ma che si era poi dedicata anche alla produzione di altri tipi di chip quando quest'ultima, per ridurre i costi dei suoi prodotti, aveva iniziato a prodursi in proprio gli integrati. Uno dei prodotti più diffusi di MOS Technology era una replica su un singolo chip del popolare gioco Pong. Nel mese di agosto del 1974 Peddle ed altri 7 ingegneri Motorola entrarono a lavorare presso MOS Technology: Bill Mensch, Harry Bawcum, Ray Hirt, Terry Holdt, Mike James, Will Mathis e Rod Orgill.[4]

Peddle ed il suo gruppo terminarono lo sviluppo della loro idea che prese corpo in 2 nuovi microprocessori che erano compatibili con i chip periferici di Motorola: il MOS 6501, progettato da Rod Orgill, che poteva essere inserito negli zoccoli del 6800 perché compatibile a livello di piedinatura con quest'ultimo, ed il MOS 6502, progettato da Bill Mensch, simile al precedente ma con una piedinatura differente ed un circuito generatore di clock integrato. Questi chip non potevano eseguire i programmi scritti per il 6800 perché avevano un'architettura ed un insieme di istruzioni differenti.

I nuovi processori furono largamente pubblicizzati su diverse riviste del settore: un annuncio apparve sul numero di luglio di Electronics[11], un altro su quello di agosto di EE Times,[12]; seguirono poi altri annunci su EDN (20/09/1975), Electronic News (03/11/1975) e Byte (novembre 1975). Annunci del 6501 apparvero in diverse pubblicazioni durante il mese di agosto del 1975: MOS Technology annunciava la presentazione del chip alla fiera dell'elettronica WESCON di San Francisco, che si sarebbe tenuta dal 16 al 19 settembre del 1975, dove sarebbe stato possibile acquistare il microprocessore a $ 25.[13] Nel mese di settembre gli annunci riguardavano anche il 6502, che veniva annunciato disponibile sempre durante il WESCON a $ 25 mentre il 6501 veniva riprezzato a $ 20.[14]

La presentazione del 6502

[modifica | modifica wikitesto]

Al WESCON il 6502 fu prezzato a $ 25. MOS Technology aveva uno stand con un grosso contenitore pieno di chip. Dato che non era riuscita a portare un numero sufficiente di esemplari funzionanti, decise di riempire il contenitore con i chip difettosi e mettere quelli funzionanti in cima, dando così l'impressione che i propri stabilimenti fossero già in grado di reggere una produzione in quantitativi industriali.[15] Nella stessa fiera il 6800 e l'Intel 8080 erano in vendita a $ 179.[16] Il MOS 6502, messo in vendita ad un prezzo di 25 dollari,[14] era la più economica CPU disponibile sul mercato, costando meno di un sesto dei modelli concorrenti: ad esempio, il Motorola 6800 era venduto a $ 175.[17] All'inizio le persone pensarono che il prezzo del 6502 fosse sbagliato o ci fosse dietro un imbroglio ma durante lo svolgimento della fiera esse videro che sia Motorola che Intel abbassarono il prezzo dei loro chip a $ 69.[18][19]

Questa riduzione dei prezzi legittimò il 6502, che cominciò ad essere venduto a centinaia di unità.[15]

La causa tra Motorola e MOS Technology

[modifica | modifica wikitesto]Dopo il WESCON MOS Technology fu citata nel mese di novembre del 1975 da Motorola:[20] quest'ultima affermava infatti che i suoi 8 ex-dipendenti avevano utilizzato informazioni tecniche sviluppate presso i propri uffici per progettare i microprocessori 6501 e 6502. Ricevuta la citazione il finanziatore di MOS Technology, Allen-Bradley, considerando anche che l'altro settore di interesse di MOS Technology, i chip per calcolatrici, non andava bene a causa di una guerra dei prezzi intentata da Texas Instruments contro gli altri produttori, decise di limitare le possibili perdite e cedette le proprie quote ai fondatori della società.[4]

La causa si risolse nel mese di maggio del 1976 con MOS Technology che decise di eliminare il chip 6501 che poteva essere montato negli zoccoli del 6800 e di acquistare le licenze dei chip periferici di Motorola.[21][22]

Il MOS KIM-1

[modifica | modifica wikitesto]

Sistemate le questioni legali ed ottenuto un buon riscontro al WESCON, MOS doveva pensare a come spingere gli sviluppatori a provare il suo nuovo processore 6502. Peddle sviluppò quindi un minicomputer denominato MDT-650 (da "Microcomputer Development Terminal") mentre un altro gruppo progettò il KIM-1. Il KIM-1 fu messo in commercio e, con stupore dei suoi progettisti, fu acquistato non solo da ingegneri ed addetti ai lavori ma anche da molti hobbisti. Anche altri sistemi simili, come il SYM-1 di Synertek ed il più flessibile AIM 65 di Rockwell (che producevano entrambe il 6502 su licenza), riscossero lo stesso buon successo commerciale.

Impiego ed utilizzo

[modifica | modifica wikitesto]Informatica

[modifica | modifica wikitesto]Uno dei primi impieghi del nuovo processore fu come CPU del computer Apple I presentato nel 1976 dalla neonata Apple, una società fondata da Steve Jobs e Steve Wozniak. Il 6502 fu poi utilizzato nel Commodore PET e nell'Apple II del 1977, ed in diversi altri computer ad 8 bit tra cui la famiglia di computer Atari ad 8 bit, la serie BBC Micro derivata dai sistemi ad 8 bit della Acorn Computers, il Commodore VIC-20 ed i computer di Ohio Scientific e Oric.[23] Il Commodore 64 usava un derivato del 6502, il MOS 6510, ma la sua unità a dischi modello 1541 usava un 6502 a 2 MHz per eseguire il codice del DOS integrato nell'unità stessa e doveva essere veloce (il doppio della CPU dell'unità C64) per rispondere alle necessità temporali del trasferimento dei dati dal floppy.

Industria

[modifica | modifica wikitesto]Agli usi civili e ludici si affiancò una notevole produzione di sistemi di controllo, anche industriale, data l'assenza dei microcontrollori di qualità (il mediocre 8048 data 1976 e spesso aveva prestazioni inadeguate). Oggi è ancora prodotto come processore per sistemi embedded da Western Design Center, una società fondata da Bill Mensch, uno dei progettisti del chip originale.

Videogiochi

[modifica | modifica wikitesto]Un altro impiego importante del 6502 e dei suoi derivati fu negli apparati videoludici. Il primo di tali apparecchi che usò un chip della famiglia 6502 fu la console Atari 2600: essa utilizzava il MOS 6507, una versione depotenziata del 6502 con un bus indirizzi ridotto ed un risultante package con soli 28 piedini. A causa di tale limitazione, il 6507 poteva indirizzare solo 8 KB di memoria, ma il package ridotto ne riduceva le dimensioni ed il costo. Nonostante ciò, l'Atari 2600 è stata venduta in 30 milioni di esemplari, ognuna con un 6507 al suo interno.

Un'altra console basata su un chip derivato dal 6502 fu la popolare Nintendo Famicom, presentata da Nintendo nel 1983: La versione per la console era prodotta da Ricoh che rispetto al progetto originale, non gestiva l'artimetica BCD ma offriva 22 registri aggiuntivi (mappati in memoria) per la gestione del suono, la lettura dei gamepad e l'accesso diretto alla memoria per gli sprite. Tale chip, chiamato 2A03 nei sistemi NTSC e 2A07 in quelli PAL (la differenza risiedeva nel diverso divisore interno del clock usato per generare l'immagine ed il suono a causa della differente frequenza dei segnali PAL e NTSC), fu prodotto esclusivamente per Nintendo.

Gli stessi arcade, molto diffusi all'epoca, erano dotati di uno o più processori, spesso il 6502, e la Atari usava quasi esclusivamente questa CPU sebbene ad alcuni tra cui il Tempest od il Battlezone aggiungeva un coprocessore basato su bit slice AMD Am2900 a causa dell'insufficiente potenza di calcolo del 6502 dovendo operare in tempo reale

Descrizione

[modifica | modifica wikitesto]

Il 6502 è un processore ad 8 bit con un bus indirizzi a 16 bit, capace quindi di indirizzare direttamente fino a 64 KB di memoria. Internamente lavora alla stessa velocità impostata dal clock esterno, tipicamente da 1 a 2 MHz: ad esempio, lo Zilog Z80 divide internamente il clock esterno per 4. Nonostante il clock inferiore le sue prestazioni sono equiparabili a quelle di altre CPU con frequenze maggiori: ciò è dovuto alla particolare architettura interna adottata, basata su una pipeline statica e sul fatto che opera con un ciclo a 2 fasi e non contando i cicli di clock. Come molte altre CPU dell'epoca, la logica NMOS del 6502 non è sequenziata da microcodice residente in ROM ma usa per la decodifica e la sequenziazione delle istruzioni un PLA preprogrammato a livello maschera (che occupa circa il 15% della superficie del chip). Come altri microprocessori ad 8 bit, il 6502 esegue una limitata sovrapposizione delle operazioni di fetch ed esecuzione delle istruzioni.

La bassa frequenza di clock riduceva i vincoli sulle velocità delle periferiche collegate alla CPU, dato che solo il 50% del ciclo di clock era disponibile per l'accesso alla memoria (a causa del progetto asincrono della CPU, questa percentuale varia molto tra le diverse versioni del chip). Ciò era importante in un periodo in cui le memorie affidabili avevano tempi di accesso nell'ordine dei 450-250 ns. Il 6502 era stato progettato per essere infatti semplice ed economico, ed abbassare i costi dell'intero sistema era un fattore molto importante per concorrere nei mercati degli home computer e delle console per videogiochi.

Come il suo precursore, il Motorola 6800, il 6502 aveva pochi registri: all'epoca in cui il 6502 fu progettato il numero di transistor contenuti in un integrato influivano molto sul suo costo e mantenerne il loro numero basso contribuiva a contenere i costi. Inoltre la RAM esterna era più veloce di una CPU, quindi era sensato ottimizzare l'architettura per l'accesso alla memoria piuttosto che incrementare il numero dei registri del chip. Il 6502 fu progettato con l'obiettivo di essere molto economico: perciò furono usati circa 4.000 transistor contro i circa 2.300 dell'Intel 4004 del 1971 ed i circa 8.500 dello Z80.[24]

Il progetto originario del 6800 prevedeva una superficie di silicio di 4.572 mm di lato pari a 20,9 mm² diventati 5.4 mm pari a 29 mm² [25] mentre il progetto del 6502 prevedeva 3.9 x 4.3 mm pari a 16.6 mm².

I registri del 6502 includono:

- 1 accumulatore ad 8 bit (registro "A");

- 2 registri indice ad 8 bit (registri "X" e "Y");

- 1 registro di stato ad 8 bit (registro "P");

- 1 puntatore di stack (registro "S") ad 8 bit (il 6800 lo aveva a 16 bit);

- 1 puntatore di programma (registro "PC") a 16 bit.

Lo stack è mappato in memoria sulla pagina 1 (indirizzi da $0100 a $01FF, 256-511). Il software accede allo stack tramite 4 istruzioni che permettono di inserire (PUSH) o recuperare (PULL) il valore dell'accumulatore o del registro di stato. Lo stesso stack è usato dalle istruzioni di gestione delle sub-routine JSR (Jump to SubRoutine) e RTS (ReTurn from Subroutine) nonché dalle routine di gestione degli interrupt.

Il 6502 usa il registro di stack e quelli indice con diverse modalità di indirizzamento, inclusa una veloce modalità detta "pagina diretta" o "pagina zero", simile a quella del PDP-8, che permette di accedere alle locazioni di memoria della pagina zero (indirizzi $0000-$00FF, 0-255) con l'uso di un indirizzo composto da solo 8 bit, risparmiando il ciclo normalmente richiesto per caricare il byte alto dell'indirizzo nel registro indice. Molto del codice scritto per il 6502 sfrutta spesso tale particolarità ed usa tali locazioni di memoria alla stregua di come sulle altre CPU vengono usati i registri interni. Su alcuni computer basati sul 6502, come il Commodore VIC-20, il sistema operativo usava quasi tutte le locazioni della pagina zero, lasciandone poche libere all'utente.[26]

Le modalità di indirizzamento sono inoltre "sottintese", concorrendo per 1 byte alla dimensione dell'istruzione. Esse sono (tra parentesi l'occupazione totale di memoria):

- absolute, "assoluta" (3 byte)

- indexed absolute, "indicizzata assoluta" (3 byte)

- indexed zero-page, "indicizzata su pagina zero" (2 byte)

- relative, "relativa" (2 byte)

- accumulator, "accumulatore (1 byte)

- indirect,x, "indiretta,x", e indirect,y, "indiretta,y" (2 byte)

- immediate, "immediata" (2 byte)

La modalità assoluta è una modalità di uso generico: le istruzioni di salto usano un indirizzo ad 8 bit con segno nell'intervallo -128 / +127, indicando quindi un indirizzo fino a 128 byte prima o 127 byte dopo l'istruzione di indirizzamento (che si traduce nell'intervallo -126 / +129 rispetto alla cella di inizio dell'istruzione di salto). La modalità accumulatore usa invece l'accumulatore come un indirizzo effettivo e non richiede nessun dato come operando. La modalità immediata usa un operando letterale ad 8 bit.

Le modalità indirette sono utili per iterazioni e per processare array di dati. Con la modalità "(indirect),y" a 5/6 cicli, il registro Y ad 8 bit viene sommato ad un indirizzo a 16 bit nella pagina zero indicato da 1 solo byte seguito dall'opcode. Il registro Y è per questo un registro "indice" nel senso che viene usato per memorizzare l'attuale "indice", a differenza del registro X del 6800 dove un indirizzo base è immagazzinato direttamente ed a cui un offset può accedere direttamente). Per incrementare il registro indice e scorrere l'array byte per byte vengono impiegati solo 2 cicli in più. Nella poco frequente modalità "(indirect),x" l'indirizzo effettivo per l'operazione viene trovato in pagina zero all'indirizzo composto aggiungendo il secondo byte dell'istruzione al contenuto del registro X. Usando le modalità indicizzate, la pagina zero opera proprio come un insieme di 128 registri indice aggiuntivi.

Il 6502 è capace di eseguire operazioni di addizione e sottrazione sia binarie che BCD. Ponendo la CPU in modalità BCD con l'istruzione SED i risultati delle operazioni vengono espressi in formato decimale: ad esempio, la somma $99 + $01 restituisce $00 con il flag del resto che viene impostato a 1, mentre in modalità binaria (istruzione CLD) la stessa operazione restituisce $9A con il flag del resto che viene impostato a 0. A parte l'Atari BASIC, tale modalità fu usata molto raramente negli home computer.

Il 6502 è stato anche indicato come uno dei primi processori RISC",[27][28] per via del suo set di istruzioni efficiente, semplice e quasi ortogonale (molte istruzioni possono operare con differenti modalità di indirizzamento) nonché per i suoi 256 "registri" in pagina zero. Il 6502 tecnicamente non è comunque un processore RISC dato che le operazioni matematiche possono leggere qualunque cella di memoria (non solo quelle in pagina zero) e diverse istruzioni (come INC, ROL, ecc...) modificano anche la memoria, contrariamente alla filosofia RISC del "load/store". Inoltre l'ortogonalità delle istruzioni è altrettanto spesso associata a "CISC". In termini di prestazioni il 6502 si comportava comunque bene, se paragonato ad altre CPU dell'epoca come lo Z80, che usava un clock molto più alto (tipicamente 3,5-4 MHz) ed il 6502 è accreditato di essere l'ispiratore di processori RISC come gli ARM,[28] anche se tale ispirazione era circoscritta alla semplice implementazione piuttosto che all'architettura, che è molto diversa rispetto a quella degli ARM.

Esempio di codice

[modifica | modifica wikitesto]Quello che segue è il classico programma Hello world scritto in codice assembly 6502 per i computer con KERNAL Commodore:

A_CR = $0D ;ritorno a capo

BSOUT = $FFD2 ;routine in ROM del Kernal che scrive sul dispositivo di output

;

LDX #$00 ;inizializza l'indice nel registro X

;

LOOP LDA MSG,X ;legge il messaggio testuale

BEQ LOOPEND ;fine del messaggio

;

JSR BSOUT ;stampa un carattere

INX

BNE LOOP ;ripete

;

LOOPEND RTS ;esce dalla subroutine

;

MSG .BYT 'Hello, world!',A_CR,$00

Interfacce dedicate

[modifica | modifica wikitesto]Ad esclusione del MOS 6522 e di pochi altri componenti, MOS Technology usò chip periferici derivati da quelli della famiglia 6800:

- MOS 6520 PIA (Parallel Interface Adapter) - quasi clone del Motorola 6821 Motorola: ha 2 porte ad 8 bit con direzionalità indirizzabile al bit

- MOS 6522 VIA (Versatile Interface Adapter) - è il 6520 con l'aggiunta di porte seriali, timer ed altri notevoli miglioramenti. All'epoca costava circa ¼ del Motorola 6821

- MOS 6526 CIA (Complex Interface Adapter)- evoluzione del 6522, fu usato sul Commodore 64 per le interfacce esterne e per gestire la tastiera

- MOS 6545 CRTC (CRT Controller)- porta video con lievissime estensioni rispetto al Motorola 6845 (come sempre per motivi legali)

- MOS 6551 ACIA (Asynchronous Communications Interface Adapter) - derivato dal Motorola 6850, espleta i servizi di UART e gestisce il protocollo RS-232

Varianti e derivati

[modifica | modifica wikitesto]Del 6502 furono prodotte diversi varianti e chip derivati:

- MOS 6507: presentava un bus indirizzi ridotto capace di indirizzare solo 8 KB. Questo chip fu usato solo nella console Atari 2600.[29]

- MOS 6509: il bus indirizzi fu esteso a 20 bit. Con l'integrazione sul chip della circuiteria per la gestione del bank switching, il 6509 poteva indirizzare fino ad 1 MB di memoria. Fu usato solo sui Commodore CBM-II.[30]

- MOS 6510: fu usato come CPU del popolare Commodore 64. Rispetto al 6502 presentava una porta I/O aggiuntiva ed un pin per l'uscita del segnale di clock.

- WDC 65C02: fabbricato da Western Design Center, era un 6502 in tecnologia CMOS con più opcode ed alcuni bug del progetto originale corretti (come ad esempio alcuni flag che non venivano, contrariamente alla documentazione, aggiornati dopo determinate operazioni).

- Ricoh 2A03: variante del 6502 senza la modalità BCD, usata esclusivamente nella console Nintendo Entertainment System.[31]

MOS 6512

[modifica | modifica wikitesto]Il MOS 6512 è una variante che lavora con un clock esterno: il 6502 originale utilizza, infatti, un generatore interno per creare i segnali di clock "Phase 1" (Φ1) e "Phase 2" (Φ2). Fu usato nel BBC Micro B+64, dove l'utilizzo del clock esterno permetteva di far lavorare normalmente la CPU a 2 MHz, per portarla ad 1 MHz quando doveva accedere a periferiche lente quali il bus di espansione, l'ADC (Analog to Digital Converter) ed il VIA.[32]

Derivati a 16 bit

[modifica | modifica wikitesto]Western Design Center progettò anche una versione a 16 bit bit del 65C02, il WDC 65C816, nonché il WDC 68C082, una versione ibrida basata su un core 65C816 capace di indirizzare 64 KB di memoria e con una piedinatura compatibile con quella del 6502/65C02: esso poteva sostituire quest'ultimo e funzionava come un normale 65C02 ma poteva anche essere configurato via software per funzionare con i registri interni "A" e "X" a 16 bit. Il 65C802 non ha avuto molta diffusione e non è più in produzione. Il 65C816 è stato usato nella console Super Nintendo Entertainment System e nell'Apple IIGS ed è ancora in produzione.[33]

Mitsubishi realizzò il 65816, un microcontrollore con un'architettura simile a quella del 65C816, anche se non compatibile al 100% con essa.

Synertek pubblicò la scheda tecnica dell'SY6516, una versione a 16 bit del 6502 che però non fu mai messa in commercio.[34]

Problemi nel progetto

[modifica | modifica wikitesto]Il progetto originale del 6502 ed i suoi derivati sono noti per avere un certo numero di istruzioni non documentate, che variano molto da un chip all'altro a seconda del produttore. Nel 6502 la decodifica delle istruzioni è implementata in una logica programmabile (simile ad un PLA) che definisce solo 151 dei 256 possibili opcode: i restanti 105 causano strani ed imprevedibili effetti (ad esempio il blocco immediato del processore, l'esecuzione di diverse operazioni valide contemporaneamente) oppure semplicemente non eseguono nulla. Eastern House Software sviluppò il "Trap65", un dispositivo che poteva essere inserito fra il processore ed il suo zoccolo per catturare questi opcode non documentati e convertirli in istruzioni BRK (che generano un interrupt software). Alcuni programmatori utilizzarono questa caratteristica per estendere il set di istruzioni del 6502 scrivendo delle routine per gli opcode non documentati che erano eseguite intercettando i vettori dell'istruzione BRK, posti all'indirizzo $FFFE. Western Design Center sostituì invece nel suo 65C02 tutti gli opcode illegali con istruzioni NOP, anche se con tempi di esecuzione ed occupazione in byte differenti.

L'istruzione di salto indiretto JMP (byte basso dell'indirizzo) ha un caso in cui non funziona come previsto: se byte basso dell'indirizzo contiene il valore $FF (quindi ogni indirizzo nel formato $xxFF), il processore non eseguirà l'istruzione all'indirizzo memorizzato in $xxFF/$xxFF+1 ma a quello memorizzato in $xxFF/$xx00. Questo bug affligge tutti chip in versione NMOS ma non i 6502 ed i suoi derivati realizzati in logica CMOS.[35]

La modalità di indirizzamento indiretta basata sul registro Y ((Ind),Y) è parzialmente difettosa. Se l'indirizzo in pagina zero è $FF (ossia l'ultima locazione di memoria della pagina zero) il processore non esegue i dati dall'indirizzo puntato da $00FF e $0100 + Y ma invece da $00FF e $0000 + Y. Tutti i chip in logica NMOS sono affetti da questo bug, che è stato corretto in molti di quelli in logica CMOS, tranne il 65C02.

La modalità di indirizzamento indiretta basata sul registro X ((Ind),X) è anch'essa difettosa se l'indirizzo in pagina zero è $FF: il problema è identico al precedente caso.

La modalità di indirizzamento indicizzata delle versioni NMOS del 6502 presentano tutte un problema nel caso di indirizzi ai margini delle pagine: in questo caso viene effettuata una lettura supplementare di un indirizzo non valido. Questo bug può causare dei problemi nel caso in cui si acceda ad hardware che opera durante una lettura (ad esempio azzerando un timer o i flag di IRQ, inviando un segnale di sincronizzazione su una linea I/O, ecc...). Questo bug è stato corretto nelle versioni CMOS, in cui il processore esegue una lettura supplementare del byte dell'ultima istruzione.

Le istruzioni di lettura/modifica/scrittura ad un particolare indirizzo eseguono 1 ciclo di lettura e 2 di scrittura. Ciò può causare problemi durante il secondo ciclo di scrittura nel caso si acceda ad hardware che opera durante la scrittura. Questo difetto è stato risolto nella versione CMOS del 6502, in cui il processore esegue 2 cicli di lettura ed 1 di scrittura.

I flag di stato "N" (risultato negativo), "V" (segnalazione di overflow) e "Z" (risultato pari a zero) non sono validi quando il processore esegue operazioni aritmetiche in modalità BCD, dato che questi flag riflettono lo stato delle operazioni in modalità binaria e non in quella BCD. Questa limitazione è stata rimossa nelle versioni CMOS. Questo bug è stato in passato utilizzato come test per verificare se la CPU fosse in logica NMOS oppure CMOS.[36]

Quando il processore si trova in modalità BCD mentre viene eseguito un interrupt hardware, esso non torna in modalità binaria. Questo difetto può generare nel codice delle routine di interrupt dei bug difficili da scovare se esse non deselezionano la modalità BCD prima di eseguire qualunque operazione aritmetica. Un sistema operativo affetto da questo problema era il KERNAL del Commodore 64, che non gestiva correttamente questo difetto del processore. Anch'esso fu risolto nelle versioni CMOS.

Il pin "SO" (Set Overflow) era stato concepito per essere usato nei driver per dispositivi ad alta velocità: quando veniva applicata una tensione (segnale "HIGH") il flag di overflow "V" del processore veniva impostato immediatamente a 1. Se tale caratteristica avesse funzionato bene, essa avrebbe eliminato un'istruzione di caricamento dal driver del dispositivo, riducendo il numero di istruzioni in un ciclo di trasferimento dati del 25%, controllando ovviamente molto accuratamente il progetto del sistema per evitare di non alterare il processo di calcolo. In pratica, però, tale caratteristica non fu praticamente mai usata.

Il set di istruzioni del 6502 include BRK) (opcode $00), che tecnicamente è un interrupt software (simile all'istruzione SWI del Motorola 6800 e dei processori ARM). BRK è spesso usata per interrompere l'esecuzione di un programma ed avviare un editor in linguaggio macchina per il test ed il debugging durante lo sviluppo del software. Può essere anche usata per instradare l'esecuzione del programma usando una semplice tabella di salto (similmente a come l'Intel 8088 ed i suoi derivati gestiscono gli interrupt software tramite un numero). Sfortunatamente, se si verifica un interrupt hardware mentre il processore sta eseguendo un'istruzione BRK allora il 6502 ignora quest'ultima ed esegue direttamente il primo. Questo difetto è stato corretto nelle versioni CMOS del processore.

Anche se non sono propriamente un bug, i comportamenti delle istruzioni JSR (Jump to SubRoutine) e RTS (ReTurn from Subroutine) possono sorprendere. L'indirizzo del punto da cui si esegue il salto inserito nello stack da JSR e recuperato poi da RTS per riprendere l'esecuzione è quello dell'ultimo byte della stessa istruzione JSR e non quello dell'indirizzo dell'istruzione successiva. Ciò accade perché la copia del valore (dal registro "PC" allo stack e viceversa) viene eseguito prima che sia incrementato automaticamente il registro puntatore di programma "PC", operazione che viene eseguita al termine di ogni istruzione. Questo modo di operare non inficia però la corretta esecuzione del salto perché l'indirizzo memorizzato in anticipo nello stack viene poi aggiornato con un incremento di 1 al termine dell'istruzione RTS.[37] Questa caratteristica non viene solitamente notata a meno che non si estragga l'indirizzo di rientro per prelevare dei parametri nel flusso del codice (una pratica comune nella programmazione del 6502). Tutti i derivati del 6502 presentano questo comportamento.

Una limitazione dello stack è il fatto che il suo puntatore "S" è ad 8 bit, per cui lo stack può contenere solo 256 valori.

Cloni nel Blocco Sovietico

[modifica | modifica wikitesto]Nel Blocco Sovietico venne prodotto un gran numero di microprocessori clonati da quelli Occidentali e tra questi il CM630 o CM630P fu un puro clone del 6502 realizzato dalla MICRO ELEKTRONIKA BULGARIA

Acceleratori

[modifica | modifica wikitesto]Diversi utenti iniziarono a cercare modi di velocizzare i propri computer. Siccome il 6502 preleva il clock dall'esterno, aumentarne la velocità era più semplice che cercare un chip più veloce che fosse compatibile. Molti costruttori iniziarono a fabbricare dispositivi "acceleratori" composti da un piccolo quantitativo di RAM ad alta velocità e dalla circuiteria necessaria a sincronizzare il 6502 "accelerato" con la RAM e le periferiche originali dei computer. Ad esempio, il floppy disk drive dell'Apple II aveva tempi di accesso molto precisi, sincronizzati tramite la gestione diretta dei registri di I/O del processore: per questo motivo gli acceleratori per l'Apple II riportavano la frequenza della CPU al valore originale di 1 MHz durante le operazioni di accesso ai dischi.

I primi acceleratori furono realizzati come schede aggiuntive ma diversi acceleratori che comparvero in seguito integrarono in un package delle dimensioni del chip originale non solo il 6502 ma anche tutta la circuiteria accessoria. Un esempio di questo tipo di acceleratori è lo Zip Chip per l'Apple II, che in un unico package inseribile nello zoccolo del 6502 in formato DIP40 integrava la CPU e 350 circuiti accessori. Lo Zip Chip elevava la frequenza del 6502 a 4 od 8 MHz, a seconda dei modelli.[38][39]

Simulatori

[modifica | modifica wikitesto]Un simulatore funzionante del 6502 è stato realizzato in JavaScript dal gruppo visual6502.org utilizzando la tecnica del reverse engineering. Infatti gli schemi tecnici originali della MOS sono stati disegnati a mano e andati perduti. Il gruppo diretto da Michael Steil è riuscito nell'intento ricavando delle immagini ad alta definizione dei vari strati del processore mediante acidi e fotografando gli stessi mediante micro fotografia. Il tutto è stato presentato alla ventisettesima edizione del Chaos Communication Congress a Berlino.[40][41][42][43]

Nella cultura di massa

[modifica | modifica wikitesto]Nel film di fantascienza Terminator (1984) ad un certo punto viene proiettato sullo schermo ciò che il robot T-800 vede attraverso i suoi occhi artificiali: all'immagine appare sovrapposto del codice assembly del 6502, che proviene da alcuni programmi per l'Apple II, di cui uno comparso su una rivista per computer denominata Nibble.[44]

Nella sitcom animata Futurama il co-protagonista Bender, un robot androide del 4° millennio, afferma in una puntata di possedere un 6502 come "cervello". David X. Cohen, produttore televisivo e principale autore della serie ha affermato che lui ed i suoi amici David Borden e David Schiminovich scrissero durante il periodo scolastico un compilatore in assembly 6502 per un linguaggio di loro creazione (chiamato "FLEET") per l'Apple II Plus, e ciò lo ha portato ad inserire detta citazione nella sitcom.[45]

Galleria d'immagini

[modifica | modifica wikitesto]-

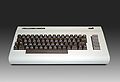

Commodore VIC-20 (1981)

-

BBC Micro (1982)

-

Apple IIe (1983)

-

Nintendo Entertainment System (1983)

(montava una CPU derivata dal 6502) -

Atari 800XL (1983)

Note

[modifica | modifica wikitesto]- ^ Longley, Shain, p. 147.(EN)

«Until recently 8 bit machines were dominated by two microprocessors — the Z80 and the 6502»

(IT)«Fino a poco tempo fa le macchine ad 8 bit furono dominate da 2 microprocessori: lo Z80 ed il 6502.»

- ^ MOS 6510, su cpu-collection.de. URL consultato il 24 settembre 2015.(EN)

«The MOS6510 is a 6502 with an additional 6 Bit bidirectional I/O Port. (…) The 6510 that was built in the C64 ran at 1 Mhz (…)»

(IT)«Il MOS 6510 è un 6502 con una porta I/O a 6 bit aggiuntiva. (…) Il 6510 che era incluso nel C64 lavorava a 1 MHz (…)»

- ^ Scheda tecnica del MOS 6510, Commodore Semiconductor Group.(EN)

«The internal processor architecture is identical to the Commodore Semiconductor Group 6502 to provide software compatibility.»

(IT)«L'architettura interna del processore è identica a quella del Commodore Semiconductor Group 6502 per garantire la compatibilità software.»

- ^ a b c Brian Bagnall, 1 e 2, in On the Edge: The Spectacular Rise And Fall of Commodore, Winnipeg, Manitoba, Variant Press, 2006, pp. 9–12, ISBN 0-9738649-0-7.

- ^ Motorola 6800 Oral History, su computerhistory.org, 2008, p. 18. URL consultato il 7 febbraio 2011 (archiviato dall'url originale il 2 aprile 2012).

- ^ a b Ian Matthews, The Rise of MOS Technology & The 6502, su commodore.ca, 26 giugno 2006. URL consultato il 6 febbraio 2011 (archiviato dall'url originale il 4 ottobre 2018).

- ^ Robert Sugarman, Does the Country Need A Good $20 Microprocessor? (PDF), in Electronic Engineering Times, 25 agosto 1975, p. 25. URL consultato il 6 febbraio 2011 (archiviato dall'url originale il 3 febbraio 2007).

- ^ (EN) Section One: Before the Great Dark Cloud - Part V: The 650x, Another Direction (1975)…, su cpushack.com, CPU Shack. URL consultato il 25 settembre 2015.(EN)

«Unlike the 8080 and its kind, the 6502 (and 6800) had very few registers. It was an 8 bit processor, with 16 bit address bus. Inside was one 8 bit data register, two 8 bit index registers, and an 8 bit stack pointer (stack was preset from address 256 ($100 hex) to 511 ($1FF)). It used these index and stack registers effectively, with more addressing modes, including a fast zero-page mode that accessed memory addresses from address 0 to 255 ($FF) with an 8-bit address that speeded operations (it didn't have to fetch a second byte for the address).»

(IT)«A differenza dell'[Intel]8080 e dei chip simili, il 6502 (ed il 6800) aveva molti pochi registri. Era un processore ad 8 bit, con un bus indirizzi a 16 bit. Al suo interno c'era un registro per i dati ad 8 bit, 2 registri indice ad 8 bit ed un puntatore allo stack ad 8 bit (lo stack era preimpostato dall'indirizzo 256 (esad. $100) a 511 ($1FF)). Usava questi registri indice e lo stack efficacemente, con più modalità di indirizzamento, inclusa una modalità pagina zero che accedeva gli indirizzi di memoria da 0 a 255 ($FF) con un indirizzo ad 8 bit che velocizzava le operazioni (non doveva caricare un secondo byte per l'indirizzo).»

- ^ (EN) Decimal Mode, su 6502.org. URL consultato il 25 settembre 2015.

- ^ (EN) 6500 microprocessors, Commodore Semiconductor Group.

- ^ Microprocessor line offers 4, 8,16 bits, in Electronics, vol. 48, n. 15, New York, McGraw-Hill, 24 luglio 1975, p. 118.

- ^ Robert Sugarman, Does the Country Need A Good $20 Microprocessor? (PDF), in EE Times, Manhasset, New York, CMP Publications, 25 agosto 1975, p. 25. URL consultato il 6 febbraio 2011 (archiviato dall'url originale il 3 febbraio 2007).

- ^ MOS 6501 Microprocessor beats 'em all, in Electronics, vol. 48, n. 16, New York, McGraw-Hill, 7 agosto 1975, pp. 60–61.

- ^ a b MOS 6502 the second of a low cost high performance microprocessor family (JPG), in Computer, vol. 8, n. 9, IEEE Computer Society, settembre 1975, pp. 38–39, DOI:10.1109/C-M.1975.219074.

- ^ a b Brian Bagnall, On the Edge: The Spectacular Rise and Fall of Commodore, Variant Press, 2005, p. 24.

- ^ James, James Advertisement, in Popular Electronics, vol. 8, n. 3, settembre 1975, p. 107.(EN)

«James is now Jameco Electronics. The 8080 CPU was $149.95, the 8008 CPU was 29.95. A 2102 1K bit static RAM was $4.95. Their price for a 8080A CPU was 37.95 in the June 1976 issue.»

(IT)«James è adesso Jameco Electronics. La CPU 8080 era a $ 149,95, la CPU 8008 era a $ 29,95. Un chip di RAM statica 2102 da 1 Kbit era a $ 4,95. Il loro prezzo per l'8080A era $ 37,95 nel numero di giugno del 1976.»

- ^ Motorola, All this and unbundled $69 microprocessor (JPG), in Electronics, vol. 48, n. 22, McGraw-Hill, 30 ottobre 1975, p. 11.

- ^ Motorola, All this and unbundled $69 microprocessor (JPG), in Electronics, vol. 48, n. 22, McGraw-Hill, 30 ottobre 1975, p. 11.(EN)

«The quantity one price for the MC6800 was reduced from $179 to $69. The previous price for 50 to 99 units was $125.»

(IT)«Il prezzo per un singolo MC6800 fu ridotto da $ 179 a $ 69. Il precedente prezzo per quantitativi da 50 a 99 chip era di $ 125 cad.»

- ^ Digi-Key, Pubblicità di Digi-Key, in Popular Electronics, vol. 8, n. 6, dicembre 1975, p. 124.(EN)

«The 8080A CPU was $69.50. A 2102 1K bit static RAM was $3.50. Digi-Key's price for a 8080A was $34.95 in the June 1976 issue.»

(IT)«La CPU 8080A era a $ 69,50. Un chip di RAM statica 2102 da 1 Kbit era a $ 3,50. Il prezzo di Digi-Key per un 8080A era di $ 34,95 nel numero di giugno del 1976.»

- ^ Motorola Sues MOS Technology (PDF), in Microcomputer Digest, vol. 2, n. 6, Cupertino CA, Microcomputer Associates, dicembre 1975, p. 11. URL consultato il 6 febbraio 2011 (archiviato dall'url originale il 4 luglio 2009).

- ^ MOS Technology Drops 6501 (PDF), in Microcomputer Digest, vol. 2, n. 11, Cupertino CA, Microcomputer Associates, maggio 1976, p. 4. URL consultato il 18 gennaio 2011 (archiviato dall'url originale l'8 gennaio 2011).

- ^ Mike Teener, Politics and Intrigue, in SCCS Interface, vol. 1, n. 6, Los Angeles, Southern California Computer Society, maggio 1976, p. 58.(EN)

«So Motorola sued and just recently won an out-of-court settlement that has MOS Technology paying $200,000 and stopping production on the 6501.»

(IT)«Così Motorola ha citato ed ha recentemente vinto una causa senza passare dai tribunali che ha visto MOS Technology pagare $ 200.000 e terminare la produzione del 6501.»

- ^ Inside the Atari 2600, su hardwaresecrets.com, 14 maggio 2012. URL consultato il 24 settembre 2015.(EN)

«The 6502 was widely used at the time in several microcomputers, such as the Apple II, Atari 400, Atari 800, Commodore VIC-20, and Commodore 64, just to name the most famous ones»

(IT)«Il 6502 fu ampiamente utilizzato all'epoca in diversi microcomputer, come l'Apple II, l'Atari 400, l'Atari 800, il Commodore VIC-20 ed il Commodore 64, giusto per citare i più famosi.»

- ^ "How many transistors in the 6502 processor?", su classiccmp.org, 5 maggio 2001. URL consultato il 7 febbraio 2011 (archiviato dall'url originale il 25 settembre 2010).

- ^ Motorola 6800 Oral History (2008), p. 10

- ^ Mappa della memoria del Commodore VIC-20 (TXT), su zimmers.net. URL consultato il 6 febbraio 2011.

- ^ Chip archeology, su compukituk101.blogspot.com, Compukit-101, 18 febbraio 2009. URL consultato il 7 febbraio 2011.

- ^ a b Richard Murray, RISC vs CISC, su heyrick.co.uk, 2002. URL consultato il 7 febbraio 2011.

- ^ (EN) Inside the Atari 2600, su hardwaresecrets.com, 14 maggio 2012. URL consultato il 24 settembre 2015.

(EN)

«The Atari 2600 was based on a MOS Technology 6507 microprocessor. This CPU was a stripped-down version of the 6502 microprocessor, limited to accessing only 8 KB of memory versus 64 KB as on the 6502 and without interrupt lines; otherwise they were the same CPU.»

(IT)«L'Atari 2600 era basata sul microprocessore MOS Technology 6507. Questa CPU era una versione ridotta del microprocessore 6502, limitata nell'accesso a soli 8 KB di memoria contro i 64 KB del 6502 e senza le linee di interrupt; a parte questo erano la stessa CPU.»

- ^ Commodore CBM-II, su 6502.org. URL consultato il 24 settembre 2015.

- ^ (EN) Informazioni sulla CPU Ricoh 2A03 del NES, su wiki.nesdev.com, NESdev.com. URL consultato il 24 settembre 2015.

(EN)

«The NES CPU core is based on the 6502 processor (...) It is made by Ricoh and lacks the MOS6502's decimal mode.»

(IT)«Il nocciolo della CPU del NES è basato sul processore 6502 (...) È fabbricato da Ricoh e non ha la modalità decimale del MOS 6502.»

- ^ The BBC and Master Computer Public Domain Library - Inside The BBC B+, su 8bs.com, 8-Bit Software. URL consultato il 7 febbraio 2011.

- ^ Specifiche del WDC 65C816, su westerndesigncenter.com, Western Design Center. URL consultato il 7 febbraio 2011.

- ^ "Syntertek SY6516 - The chip that never existed" (TXT), su homepage.mac.com, Apple II Things. URL consultato il 7 febbraio 2011 (archiviato dall'url originale il 28 giugno 2010).

- ^ MOS 6502, su foldoc.org, Free Online Dictionary of Computing. URL consultato il 25 giugno 2014.

- ^ Test di verifica CMOS/NMOS per i 6502, su s-direktnet.de, Pagina su Web.Archive.org. URL consultato il 7 febbraio 2011 (archiviato dall'url originale il 2 gennaio 2008).

- ^ Mark Andrews, 6, in "Atari Roots - A Guide to Atari Assembly Language", DATAMOST, Inc., 1984, ISBN 0-88190-171-7.(EN)

«RTS ("pull the return address off the stack and put it in the PC and increment it by one." This will cause execution to continue where it left off.)»

(IT)«RTS ("estrae dallo stack l'indirizzo di rientro, lo inserisce nel PC e lo incrementa di 1." Questo comporterà che l'esecuzione riprenderà da dove era stata sospesa.»

- ^ Manuale utente dello Zip Chip (PDF), ZIP Technology. URL consultato il 7 febbraio 2011 (archiviato dall'url originale l'11 settembre 2014).

- ^ Foto dello Zip Chip e della sua confezione, su nekochan.net. URL consultato il 7 febbraio 2011 (archiviato dall'url originale il 27 gennaio 2011).

- ^ 6502 Images, su visual6502.org. URL consultato il 28 novembre 2017.

- ^ (EN) CCC | Home, su ccc.de. URL consultato il 28 novembre 2017.

- ^ Christiaan008, 27c3: Reverse Engineering the MOS 6502 CPU (en), 10 gennaio 2011. URL consultato il 28 novembre 2017.

- ^ Visual 6502 in JavaScript, su visual6502.org. URL consultato il 28 novembre 2017.

- ^ "The 6502 in 'The Terminator'", su pagetable.com. URL consultato il 7 febbraio 2011.

- ^ "The Truth About Bender's Brain", su spectrum.ieee.org, IEEE, 05/2009. URL consultato il 7 febbraio 2011.

Bibliografia

[modifica | modifica wikitesto]Monografie in italiano

[modifica | modifica wikitesto]- Bob Bright, Assembler 6502, collana Tascabili, Gruppo Editoriale Jackson, 1985.

- Rodnay Zaks, Programmazione del 6502, Gruppo Editoriale Jackson, 1981.

- Rodnay Zaks, Applicazioni del 6502, Gruppo Editoriale Jackson, 1981.

- Rodnay Zaks, Giochi con il 6502, Gruppo Editoriale Jackson, 1982, ISBN 88-7056-104-6.

Monografie in inglese

[modifica | modifica wikitesto]- (EN) Lance A. Leventhal, 6502 Assembly Language Programming, 2ª ed., Osborne/McGraw-Hill, 1986, ISBN 0-07-881216-X.

- (EN) Lance A. Leventhal, 6502 Assembly Language Subroutines, Osborne/McGraw-Hill, 1982, ISBN 0-931988-59-4.

- (EN) Rodnay Zaks, Advanced 6502 Programming (PDF), Sybex, Inc., 1982, ISBN 0-89588-089-X.

- (EN) Richard Mansfield, Machine Language For Beginners - Personal Computer Machine Language Programming For The Atari, VIC, Apple, Commodore 64, And PET/CBM Computers, Greensboro, North Carolina, Compute! Publications, Inc., 1983, ISBN 0-942386-11-6.

Capitoli in opere generali

[modifica | modifica wikitesto]- Microprocessori, Gruppo Editoriale Jackson, 1988, pp. 143-162, ISBN 88-256-0068-2.

Articoli in rivista

[modifica | modifica wikitesto]- (EN) Robert Sugarman, Does the Country Need a Good $20 Microprocessor? (PDF), in Electrical Engineering Times, 25 agosto 1975, p. 25. URL consultato l'8 febbraio 2011 (archiviato il 3 febbraio 2007).

- (EN) 3rd Generation Microprocessor (PDF), in Microcomputer Digest, vol. 2, n. 2, Cupertino, California, Microcomputer Associates, 08/1975, pp. 1-3. URL consultato il 5 maggio 2021 (archiviato il 4 luglio 2009).

- (EN) Daniel Fylstra, Son of Motorola (or the $20 CPU Chip), in BYTE, vol. 1, n. 3, Peterborough, New York, Green Publishing, 11/1975, pp. 56-62.

- Parliamo un po' del 6502 (JPG), in Bit, anno 2, n. 5, Milano, Gruppo Editoriale Jackson, novembre/dicembre 1979, pp. 35-40, ISSN 0392-8837.

Altri progetti

[modifica | modifica wikitesto] Wikimedia Commons contiene immagini o altri file su MOS 6502

Wikimedia Commons contiene immagini o altri file su MOS 6502

Collegamenti esterni

[modifica | modifica wikitesto]Informazioni generali

[modifica | modifica wikitesto]- 6502.org - Risorse per il MOS 6502

- Dati e foto sulle CPU 650x (cpu-collection.de)

Caratteristiche del set di istruzioni

[modifica | modifica wikitesto]- Il set di istruzioni del 6502, su mdfs.net. URL consultato il 7 febbraio 2011 (archiviato dall'url originale il 13 gennaio 2009).

- 6502 - il primo microprocessore RISC µP, su ericclever.com. URL consultato il 7 febbraio 2011 (archiviato dall'url originale il 24 maggio 2012).

Emulatori e simulatori

[modifica | modifica wikitesto]- Simulazione visuale a livello di transistor del 6502, su visual6502.org.

- Elenco degli emulatori software del 6502 (zophar.net)

- Simulatore del 6502 per Windows (atarihq.com)

- Compilatore ed emulatore del 6502 per browser scritto in JavaScript, su 6502asm.com.

Primi computer basati sul 6502

[modifica | modifica wikitesto]- Apple I Owners Club - Club dei possessori dell'Apple I (applefritter.com)

- Schema del KIM-1 schematics (oldcomputers.net)

- Rockwell AIM 65, su oldcomputers.arcula.co.uk.

Acceleratori hardware

[modifica | modifica wikitesto]- Informazioni sugli acceleratori per il 6502 (apple2history.org)

Hardware

[modifica | modifica wikitesto]- The Western Design Center, Inc. (WDC) - Produce ancora i processori 65xx

| Controllo di autorità | LCCN (EN) sh85000011 · GND (DE) 4120731-2 · BNE (ES) XX527727 (data) · BNF (FR) cb11953064v (data) · J9U (EN, HE) 987007292977805171 |

|---|